### РАЗРАБОТКА IBIS-МОДЕЛЕЙ ЦИФРОВЫХ МИКРОСХЕМ НА ОСНОВЕ ЭКСПЕРИМЕНТАЛЬНЫХ ДАННЫХ

С. Н. Дмитриев<sup>1</sup>, Ф. Г. Зограф<sup>1</sup>, А. А. Левицкий<sup>1</sup>, П. С. Маринушкин<sup>1</sup>, М. С. Московских<sup>2</sup>,

<sup>1</sup>Сибирский федеральный университет, г. Красноярск, Российская Федерация <sup>2</sup>АО «Информационные спутниковые системы» им. академика М. Ф. Решетнёва», г. Железногорск, Красноярский край, Российская Федерация

В настоящее время для проведения анализа целостности сигналов может использоваться ряд моделей, включая IBIS (и расширение этой модели – EBD), MOD (соответствующее расширение – PML), SPICE. Модели спецификации IBIS могут применяться при проектировании быстродействующих печатных узлов во многих системах проектирования, в частности, в P-CAD 200X, Altium Designer, Mentor Graphics HyperLynx (LineSim, BoardSim) и в других программных средствах. IBIS-модели позволяют обходить трудности, связанные с созданием и применением для интегральных схем SPICEмоделей, базирующихся на подробном описании внутренней структуры устройства. В данной работе рассмотрена экспериментальная методика создания IBIS-моделей. Основное внимание уделено интерпретации измеренных вольт-амперных характеристик входных и выходных буферов цифровых интегральных схем. В качестве базовой для создания IBIS-модели выбрана структура выходного буфера цифровой схемы, выполненная по КМОП-технологии. Одним из наиболее сложных этапов в экспериментальной методике является получение корректных динамических характеристик для создания IBIS-модели. Наряду с моделированием экспериментальная методика позволяет существенно уменьшить сложность и время создания IBIS-моделей.

Ключевые слова: целостность сигналов, IBIS-модели.

#### Введение

В связи с повышением плотности печатного монтажа и возрастанием рабочих частот устройств на основе цифровых интегральных схем возрастает сложность задач по обеспечению электромагнитной совместимости радиоэлектронных устройств, включая целостность сигналов.

Для оценки искажений сигналов вследствие несогласованности сигнальных цепей и входов/выходов интегральных схем, перекрестных помех на печатной плате и других факторов применяется ряд моделей цифровых микросхем, в том числе: IBIS (Input/Output Buffer Information Specification) и ее расширение – EBD, MOD (и расширение этой модели – PML), SPICE, Touchstone [1–3]. Применение IBIS-моделей обеспечивает значительное сокращение объема расчетов по сравнению с использованием полных эквивалентных SPICE-моделей (Simulation Program with Integrated Circuit Emphasis), интегральных схем,

базирующихся на детальном описании внутренней структуры изделия [4, 5].

*IBIS*-модель — это внешнее описание электрического устройства (обычно цифровой высокоскоростной микросхемы), как «черного ящика», без учёта его внутренней структуры и особенностей функционирования. Параметры *IBIS*-моделей получают на основе вольт-амперных характеристик (ВАХ) для различных логических состояний выводов по постоянному току, паразитных параметров корпуса и переходных характеристик на резистивной нагрузке.

Моделирование с помощью *IBIS*-моделей позволяет провести оценку целостности сигналов, определить работоспособность изделия на этапе проектирования. Предтопологический и посттопологический анализ с использованием *IBIS*-моделей реализован в ряде систем проектирования печатных плат, в частности, в *P-CAD* 200X, *Altium Designer*, *Mentor Graphics HyperLynx* (*LineSim, BoardSim*).

Однако *IBIS*-модель не всегда доступна для разработчика, что характерно, в частности, для элементной базы отечественного производства [4, 5]. Поэтому возникает потребность в разработ-

<sup>©</sup> Дмитриев С. Н., Зограф Ф. Г., Левицкий А. А., Маринушкин П. С., Московских М. С., 2017 DOI: 10.26732/2225-9449-2017-4-184-192

ке методики создания *IBIS*-модели и проверки её на адекватность.

Данная работа посвящена анализу процедуры создания *IBIS*-моделей цифровых интегральных микросхем на основе экспериментальных ланных.

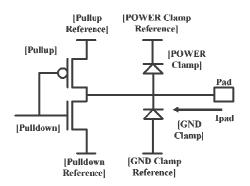

В основу *IBIS*-модели положена базовая структура буфера цифровой схемы. На рис. 1 представлен пример структуры выходного КМОП буфера, включающей следующие элементы: *GND Clamp* — элементы, описывающие BAX защитных («антизвоновых») диодов между сигнальным проводником и общим проводом («землей»); *POWER Clamp* — элементы, описывающие BAX защитных диодов между сигнальным проводником и питанием; *Pulldown* — характеристики выходной части схемы между выходом и «землей»; *Pullup* — характеристики выходной части схемы между выходом и питанием.

Технология построения *IBIS*-модели реализуется на основе таблиц, задающих BAX буферов и переходные процессы, обусловленные паразитными параметрами корпуса и входной ёмкостью кристалла. Эти характеристики можно получить из экспериментальных исследований образцов микросхем либо получить из *SPICE*-модели, для

Рис. 1. Структура выходного КМОП буфера [2]

чего необходимо иметь такую модель, что не всегда возможно.

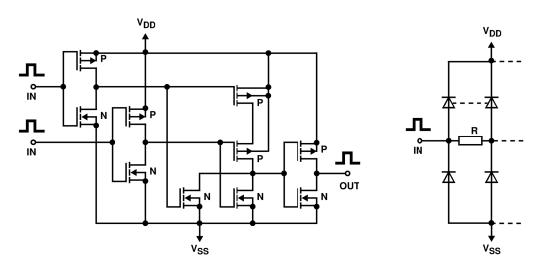

Рассмотрим порядок формирования IBIS-модели на основе экспериментальных данных на примере микросхемы CD4011BE (аналог — K561ЛА7), содержащей четыре логических элемента 2И-НЕ, выполненных по КМОП-технологии (рис. 2).

Процедура создания модели включает следующие этапы.

- 1. Определение типов выводов (входные, выходные, вход/выход).

- 2. Установка буферов в требуемое состояние (управляющими сигналами) измерения на выходах микросхемы проводятся при низком и высоком логическом уровнях.

- 3. Конфигурирование микросхемы, измерение ВАХ буферов микросхемы.

- 4. Исследование переходных процессов на выводах буферов (определяется параметр *Ramp* скорость переключения из 0 в 1 и из 1 в 0).

- 5. Определение паразитных параметров выводов (L, R, C).

- 6. Построение модели.

- 7. Проверка модели. Моделирование с использованием созданной *IBIS*-модели и сравнение результатов моделирования с измеренными данными.

## 1. Исследование статических характеристик

Рассмотрим первые три этапа для микросхемы CD4011BE.

1. Типы выводов для данной микросхемы однозначно определены в документации. В ряде случаев, например, при создании *IBIS*-модели микроконтроллера (у микроконтроллеров некоторые выводы способны работать и как вход, и как выход) может потребоваться специальная программа для перевода выводов в нужное состояние.

Рис. 2. Схема элемента 2И-НЕ микросхемы *CD4011BE* и схема диодной защиты ее входов (справа) [5]

186

- 2. Установка выводов в нужное состояние. Для того, чтобы получить на выходе логической ячейки логический ноль, на оба выхода ячейки подается напряжение 3...15 В (через дополнительный резистор). Для получения уровня логической единицы оба входа подключают к общему проводу.

- 3. Микросхема содержит в одном корпусе четыре независимых элемента 2И-НЕ, изготовленных в одном технологическом цикле, следовательно, разброс параметров будет минимальный и все измерения можно будет провести только на одном из элементов.

Измерение ВАХ служит основой для составления таблиц, которые согласно спецификации *IBIS* описываются ключевыми словами (заголовками) [Pulldown], [Pullup], [GND Clamp] и [POWER Clamp].

Буферы могут моделироваться, используя различные комбинации таблиц с ключевыми словами в зависимости от их модели [Model type] (входной - Input, выходной, - Output, ввода-вывода – I/O). Входные буферы включают только ключевые слова [GND Clamp] и/или [POWER Clamp], используемые для описания поведения защитных диодов буфера. Выходные буферы обычно содержат только таблицы [Pullup] и [Pulldown], так как характеристики их защитных цепей не могут быть выделены на фоне состояний низкого или высокого выходного логического уровня. Буферы ввода-вывода (двунаправленные) могут выдавать или принимать сигналы, и, таким образом, все четыре ключевых слова для ВАХ обычно присутствуют для этих типов.

Буфер с тремя состояниями, хотя и не способен принимать сигналы, может быть переключен в состояние «0», «1» или переведен в состояние с высоким выходным импедансом, при котором характеристики защитных цепей очевидны. В результате буферы с тремя состояниями также обычно содержат все четыре ключевых слова для ВАХ. Другие типы буферов, например с открытым стоком, содержат комбинации четырех ключевых

слов ВАХ, соответствующих их возможностям выдачи и приема сигналов.

Самой сложной задачей по окончании измерений является получение скорректированной ВАХ, необходимой для формирования *IBIS*-модели.

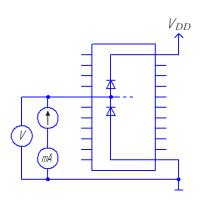

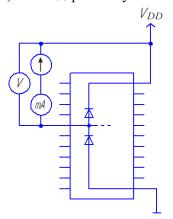

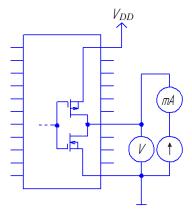

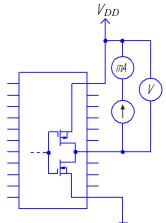

В данном случае для микросхемы *CD4011BE* входные ВАХ определяются свойствами защитной диодной цепи. Варианты схем для измерения ВАХ входных буферов представлены на рис. 3 и 4 (подключение вольтметра может изменяться в зависимости от сопротивления измеряемой цепи). Во избежание неконтролируемого разогрева микросхемы и выхода ее из строя измерения следует проводить в импульсном режиме, исключая, однако, возможное влияние на результаты паразитных реактивностей.

Следует отметить, что для *IBIS*-модели BAX буферов должны быть определены в диапазоне от отрицательного напряжения, значение которого выбирается равным напряжению питания микросхемы ( $V_{DD}$  на рис. 3), до значения, равного удвоенному напряжению питания. Полагается, что это условие необходимо выполнить для того, чтобы при анализе целостности сигналов *IBIS*-модель позволяла учитывать реакцию буфера на переотраженные сигналы, из-за которых напряжения на выводах микросхемы в наихудшем случае могут достигать максимального отрицательного амплитудного значения  $-V_{DD}$  или положительного амплитудного значения  $V_{DD} \times 2$ .

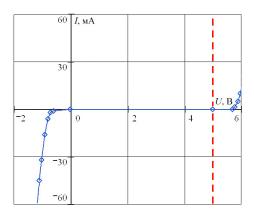

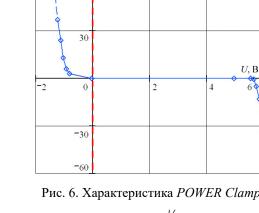

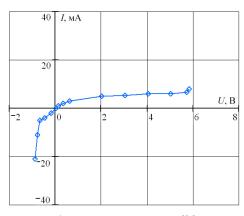

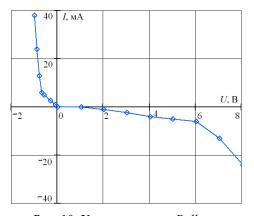

Согласно спецификации IBIS, значения напряжений в таблице [GND Clamp], измеренные относительно «земли», должны охватывать диапазон как минимум от  $-V_{DD}$  до  $V_{DD}$ . Результаты измерений для входных цепей микросхемы, полученные при напряжении питания  $V_{DD} = +5$  В, представлены на рис. 5 и 6.

Из полученной с помощью измерений таблицы [GND Clamp] для защитной цепи, связанной с «землей», следует исключить точки, в которых напряжение равно или превышает  $V_{DD}$  (см. рис. 6). Благодаря этому итоговая таблица

Рис. 3. Схема для измерения характеристики *GND Clamp*

Рис. 4. Схема для измерения характеристики *POWER Clamp*

Разработка IBIS-моделей цифровых микросхем на основе экспериментальных данных

60 I, MA

Рис. 5. Характеристика GND Clamp

Рис. 6. Характеристика POWER Clamp

Рис. 7. Схема для измерения характеристики Pulldown

Рис. 8. Схема для измерения характеристики Pullup

Рис. 9. Характеристика Pulldown

Рис. 10. Характеристика *Pullup*

BAX [GND Clamp] в IBIS-модели не содержит данных, связанных с влиянием защитной цепи [POWER Clamp].

Данные [POWER Clamp] должны охватывать как минимум диапазон от  $V_{DD}$  до  $2 \times V_{DD}$  (относительно «земли»). Соответственно в итоговой таблице напряжения, отсчитываемые относительно  $V_{DD}$ , должны изменяться в диапазоне от –  $V_{DD}$ до 0 В. Поэтому в полученной из измерений таблице ВАХ для [POWER Clamp] исключаются точки, в которых напряжение равно или более 0 В. Это гарантирует, что окончательная таблица [POWER Clamp] не содержит данных, относящихся к защитной диодной цепи, связанной с «землей».

Необходимо также отметить, что в случае буферов с ODT (On-Die Termination – встроенная «терминация» в чипе) на результаты измерений ВАХ будет оказывать влияние структура ODT. Выделение характеристик ООТ связано с дополнительными трудностями.

Схемы измерений для выходных буферов представлены на рис. 7 и 8.

Результаты измерений характеристик Pulldown и Pullup представлены на рис. 9 и 10.

188

Измерения BAX [Pulldown] выполняются в режиме, при котором выходной буфер (или буфер ввода-вывода) переведен в состояние с низким логическим уровнем. Для того, чтобы удовлетворять минимальным требованиям спецификации IBIS, данные [Pulldown] должны перекрывать диапазон от  $-V_{DD}$  до  $2 \times V_{DD}$ . Если буфер имеет тип ввод/вывод, то сначала следует вычесть токи цепей защиты из полученных путем измерений значений тока и поместить результирующие значения в таблицу [Pulldown]. В этом случае при последующем анализе работы схемы с использованием *IBIS*-модели программа-симулятор суммирует данные таблицы BAX защитных цепей с таблицей BAX [Pulldown], воспроизводя при этом исходную таблицу ВАХ [Pulldown].

Таблица [Pullup] содержит данные BAX, полученные при переключении выходного буфера (или буфера ввода-вывода) в состояние с высоким логическим уровнем. При этом так же, как и в предыдущем случае, если буфер имеет тип ввод/вывод, то следует вычесть токи цепей защиты из измеренных для выводов значений тока и ввести полученные данные в таблицу [Pullup]. В итоговой таблице данные [Pullup] также должны охватывать диапазон от  $-V_{DD}$  до  $2 \times V_{DD}$ .

## 2. Исследование динамических характеристик

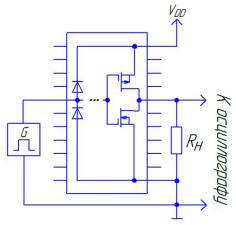

На рис. 11 представлена схема включения для исследования переходной характеристики выходного буфера микросхемы. Для измерения характеристик микросхемы *CD4011BE* использовались двухканальный цифровой осциллограф *TEKTRONIX TDS*2024*C* и генератор импульсов *PG*-872, обеспечивающий длительность фронтов импульсов не более нескольких наносекунд.

Измерения проводились при напряжении питания микросхемы 5 В. С генератора на вход

микросхемы подавались положительные прямоугольные импульсы амплитудой 5 В, длительностью 0,3–0,5 мкс, период повторения импульсов составлял 3 мкс. Длительность фронтов импульсов, вырабатываемых генератором, не превышала 2 нс. Длительность импульсов выбиралась не менее 0,1 мкс, так как при более коротких импульсах могло быть затруднено измерение переднего и заднего фронтов на выходе микросхемы.

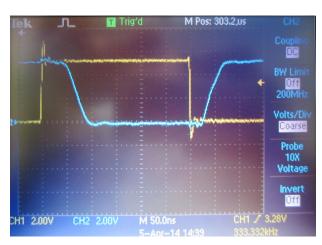

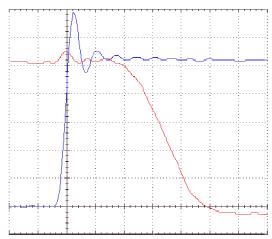

На рис. 12 приведен вид осциллограммы при сопротивлении нагрузки на выходе буфера  $R_{\rm H}=100$  кОм. На осциллограмме жёлтым цветом выделен сигнал генератора (первый канал осциллографа СН1), используемый для синхронизации осциллографа. Выбросы («звон») на фронтах импульсов являются следствием влияния соединительного кабеля, и для данных измерений эти выбросы не оказывают заметного влияния на время включения и выключения микросхемы.

Измерения показывают, что с уменьшением сопротивления нагрузки от 100 кОм до 10 кОм наблюдается небольшая (примерно 200 мВ) «просадка» амплитуды импульса и его фронт становится более «затянутым». Данное измерение показывает влияние снижения сопротивления нагрузки на параметры выходных импульсов.

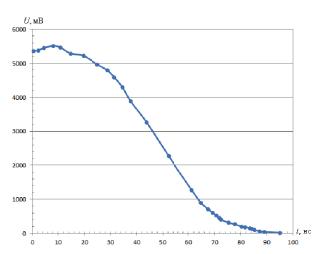

Полученные осциллограммы позволяют сформировать таблицу значений, описывающую измеренную переходную характеристику для *IBIS*-модели микросхемы. На рис. 13 приведена фрагмент осциллограммы, на которой красным цветом выделен передний фронт импульса на выходе микросхемы, а на рис. 14 показан соответствующий ему восстановленный по таблице вид сигнала.

В переходной характеристике представляют интерес крутизна фронта и его длительность. Эти параметры напрямую связаны с паразитными параметрами (L, C) кристалла микросхемы, а также её корпуса.

Рис. 11. Схема для исследования переходной характеристики выходного буфера

Рис. 12. Осциллограмма переключения буфера микросхемы при  $R_{\rm H} = 100~{\rm kOm}$

Разработка IBIS-моделей цифровых микросхем на основе экспериментальных данных

Рис. 13. Осциллограмма — передний фронт импульса (красная линия). Масштаб по вертикальной оси — 1 В/деление, по горизонтальной — 20 нс/деление

#### 3. Структура разделов файла IBIS-модели

Файл *IBIS*-модели имеет расширение \*.ibs и может создаваться и редактироваться в обычном текстовом редакторе, но более предпочтительно использование специализированной программы *Visual IBIS Editor* компании *Mentor Graphics*. Файл *IBIS*-модели состоит из трех частей с дополнительным, но не обязательным «внешним» описанием корпуса. Эти три части включают следующие данные.

- 1. Общая информация о самом файле и моделируемом компоненте.

- 2. Имя компонента, расположение выводов и их описание.

- Описания каждого уникального буфера в компоненте.

Рис. 14. Переходная характеристика, построенная по таблице значений, сформированной для *IBIS*-модели

Первый раздел файла модели, содержащий основную информацию о самом файле и размещенных в нем данных, может включать ключевые слова, представленные в табл. 1.

Ниже приведен фрагмент начала файла *IBIS*-модели микросхемы SN74AHC125, предоставляемой компанией Texas Instruments для свободного использования (http://www.ti.com/product/SN74AHC125). Как видно, в одном файле *IBIS*-модели могут одновременно содержаться характеристики для различных типов корпусов, в которых изготавливается микросхема. *IBIS*-модель SN74AHC125 содержит характеристики сразу для шести типов корпусов.

Второй раздел файла *IBIS*-модели содержит информацию о параметрах выводов буферов и корпуса микросхемы. Второй раздел начинается с названия компонента и указания его корпуса.

Таблица 1

### Параметры первой части файла IBIS-модели

| Ключевое<br>слово | Обязательный параметр (да/нет) | Описание                                                                                                                        |

|-------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| [IBIS Ver]        | Да                             | Версия спецификации IBIS, используемая в файле                                                                                  |

| [Comment char]    | Нет                            | Изменение символа комментария. По умолчанию используется символ комментария – «   »                                             |

| [File Name]       | Да                             | Название файла. Все имена файлов должны быть представлены в нижнем регистре (строчными буквами). Расширение имени файла – «ibs» |

| [File Rev]        | Да                             | Уровень ревизии файла. Спецификация <i>IBIS</i> содержит руководящие принципы для назначения уровней ревизий                    |

| [Date]            | Нет                            | Дата создания файла                                                                                                             |

| [Source]          | Нет                            | Источник данных в файле. Данные из справочника? Данные из моделирования? Измеренные?                                            |

| [Notes]           | Нет                            | Составляющие или определенные для файла примечания (поясняющие записи)                                                          |

| [Disclaimer]      | Нет                            | Правовая оговорка (сведения юридического характера)                                                                             |

| [Copyright]       | Нет                            | Уведомление об авторском праве файла                                                                                            |

TEXAS INSTRUMENTS INCORPORATED Standard Linear and Logic Group IBIS Model of SN74AHC125 QUADRUPLE BUS BUFFER GATES WITH 3-STATE OUTPUTS This file contains package information for the following: PDIP 14-pin (N) package as [Component] AHC125 N SOIC 14-pin (D) package as [Component] AHC125 D SSOP 14-pin (DB) package as [Component] AHC125\_DB TVSOP 14-pin (DGV) package as [Component] AHC125\_DGV SOP 14-pin (NS) package as [Component] AHC125\_NS TSSOP 14-pin (PW) package as [Component] AHC125\_PW This device can be powered at the following Vccs: 3.3 volt Vcc 5 volt Vcc 2.2 volt Vcc This file provides unique models under the [Model Selector] for each Vcc. For operation at a specific Vcc, select the appropriate model after each [Model Selector] keyword. [IBIS Ver] [Comment char] | char [File Name] sn74ahc125.ibs [File Rev] 1.1 | a\_die April 19, 2002 [Date] [Source] Data created from TI-SPICE simulations at TI-SLL. [Notes] The following is an IBIS list for the SN74AHC125. Please contact sllibis@ti.com with questions and comments concerning SLL IBIS models. -As there is no power clamp diode in the Input and OE Models, we removed the Pwr Clamp table data from those Models. -C comp values are taken at a different test condition than the data sheet. [Disclaimer] Property of Texas Instruments Incorporated.

Этот раздел может включать ключевые слова, приведенные в табл. 2.

Ниже приведен фрагмент второй части файла *IBIS*-модели микросхемы SN74AHC125. Как видно, в ней используются всего четыре ключевых слова.

Для измерения паразитных параметров корпуса микросхемы необходимо проведение значительного объема измерений. В случае затруднений при экспериментальном определении параметров корпуса можно использовать значения паразитных параметров корпуса для аналогичных микросхем в таком же корпусе и с подобной внутренней структурой.

Согласно синтаксису стандарта *IBIS*, данные измерений могут быть представлены в разных форматах. Допускается, например, записать параметр R\_pkg в виде «450.840m» или же в виде «4.50e-02», или же параметр L pkg записать как

«5.407nH» или «5.407e-09». Ещё пример: время в колонке «Тіте» можно указывать в формате «1.042E-09s» либо «1.042E-09» без буквы «s», но для удобства восприятия обычно используют первый вариант. При этом временной параметр может быть записан в виде «1.042nS» или «1042fS». Синтаксис стандарта *IBIS* разрешает использование размерных приставок, таких как:  $f(10^{-15})$ ;  $p(10^{-12})$ ;  $n(10^{-9})$ ;  $u(10^{-6})$ ;  $m(10^{-3})$ .

Третий раздел файла *IBIS*-модели содержит таблицы значений BAX и переходных (вольтсекундных) характеристик для каждого независимого буфера. Раздел начинается с ключевого слова [Model] — с него начинается описание данных для конкретного буфера. В то время как модель самого буфера бывает довольно сложной, описание для большинства буферов может включать всего несколько параметров и ключевых слов.

Таблица 2

#### Параметры второй части файла *IBIS*-модели

| Ключевое<br>слово  | Обязательный параметр? (да/нет) | Описание                                                                                                                                                                                                                                                        |

|--------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [Component]        | Да                              | Название описываемого моделью компонента. Общепринятая практика — использовать в названии часть промышленного обозначения компонента. Файл модели может содержать многократные [Component] описания                                                             |

| [Manufacturer]     | Да                              | Наименование производителя компонентов                                                                                                                                                                                                                          |

| [Package]          | Да                              | Ключевое слово указывает данные о диапазоне (минимальные, типичные и максимальные значения), в пределах которого может изменяться сопротивление выводов корпуса, индуктивность и емкость (параметры R_pkg, L_pkg и C_pkg)                                       |

| [Pin]              | Да                              | Ключевое слово открывает подраздел, включающий информацию о выводах буферов. Кроме того, разработчик модели может использовать это ключевое слово для перечисления значений $R$ , $L$ и $C$ каждого отдельного вывода (параметры $R$ _pin, $L$ _pin и $C$ _pin) |

| [Package<br>Model] | Нет                             | Если модель компонента включает внешнюю модель корпуса (или в файле <i>IBIS</i> используется запись [Define Package Model]), данное ключевое слово указывает имя этого корпуса модели                                                                           |

| [Pin Mapping]      | Нет                             | Ключевое слово используется, если разработчик модели желает включить информацию о цепи «питания» буфера и соединениях «земли». Эта информация может быть использована для моделирования с участием переключения нескольких выходов                              |

| [Diff Pin]         | Нет                             | Ключевое слово используется для связывания буферов, для которых должно использоваться специальное управление, здесь – дифференциальная пара                                                                                                                     |

| Com          | manant]    | AHC125 N              |           |           |           |  |

|--------------|------------|-----------------------|-----------|-----------|-----------|--|

|              |            | Texas Instrument      | s Inc     |           |           |  |

| [Pack        | -          | 1 CAGS IIISTI UIIICII | s, IIIC.  |           |           |  |

| li ack       | <i>U</i> , | p min                 | max       |           |           |  |

| ı<br>Rnk     |            | e-02 3.700e-02        |           |           |           |  |

|              |            | e-09 3.922e-09        |           |           |           |  |

| $C_{\rm pk}$ | g 3.107    | e-13 2.050e-13        | 6.040e-13 |           |           |  |

| r            | ٥٥         |                       |           |           |           |  |

| ***          | *****      | ******                | *****     | ******    | *****     |  |

| İ            |            |                       |           |           |           |  |

| [Pin]        | signal na  | me model_name         | e R pin   | L pin     | C pin     |  |

|              |            |                       |           |           |           |  |

| 1            | 1NOE       | AHC125_OE             |           |           |           |  |

| 2            | 1A         | AHC125_IN             |           |           |           |  |

| 3            | 1Y         | AHC125_OUT            | 4.200e-02 | 4.389e-09 | 3.220e-13 |  |

| 4            | 2NOE       | AHC125_OE             |           |           |           |  |

| 5            | 2A         | AHC125_IN             | 3.900e-02 | 4.301e-09 | 2.980e-13 |  |

| 6            | 2Y         | AHC125_OUT            | 3.800e-02 | 5.329e-09 | 3.560e-13 |  |

| 7            | GND        | GND                   |           | 6.510e-09 | 5.440e-13 |  |

| 8            | 3Y         | AHC125_OUT            |           | 6.437e-09 |           |  |

| 9            | 3A         | AHC125_IN             |           | 5.352e-09 |           |  |

| 10           | 3NOE       | AHC125_OE             |           |           |           |  |

| 11           | 4Y         | AHC125_OUT            |           |           |           |  |

| 12           |            | AHC125_IN             |           |           |           |  |

| 13           |            | AHC125_OE             |           |           |           |  |

| 14           | VCC        | POWER                 | 6.100e-02 | 6.900e-09 | 6.030e-13 |  |

### Список литературы

- 1. Baker B. The IBIS model: A conduit into signal-integrity analysis, Part 1. *Analog Applications Journal* (4Q 2010). Available at: www.ti.com/lit/an/slyt390/slyt390.pdf

- 2. The IBIS Open Forum. IBIS Modeling Cookbook for IBIS Version 4.0. Available at: http://ibis.org/cookbook/cookbook-v4.pdf

- 3. Low S. M., Shafdar M. H. Creating the IBIS model for a digital IC device. JURNAL FIZIK MALAYSIA, vol. 31, no. 1&2, 2010, pp. 1–4.

- 4. Лемешко Н. В. Разработка метода проектирования цифровых узлов радиотехнических систем с применением IBIS-моделей интегральных микросхем: дис. ... канд. техн. наук. М., 2008. 122 с.

- 5. Петросянц К. О., Харитонов И. А., Адонин А. С., Сидоров А. В., Александров А. В. Создание IBIS-моделей цифровых микросхем с учетом воздействия внешних факторов // Проблемы разработки перспективных микро- и наноэлектронных систем 2012 : сб. тр. / отв. ред. В. С. Борискин ; под общ. ред. А. Л. Стемпковского. М. : ИППМ РАН, 2012. С. 187–192.

- 6. CD4011B, CD4012B, CD4023B. Data sheet. Texas Instruments Incorporated, 2006.

История статьи

Поступила в редакцию 3 ноября 2017 г. Принята к публикации 18 ноября 2017 г.

# CREATING THE IBIS MODELS FOR A DIGITAL IC BASED ON THE EXPERIMENTAL DATA

S. N. Dmitriev<sup>1</sup>, F. G. Zograf<sup>1</sup>, A. A. Levitskiy<sup>1</sup>, P. S. Marinushkin<sup>1</sup>, M. S. Mockovskih<sup>2</sup>,

<sup>1</sup>Siberian Federal University, Krasnoyarsk, Russian Federation <sup>2</sup>JCS «Academician M. F. Reshetnev» Information Satellite Systems», Zheleznogorsk, Krasnoyarsk region, Russian Federation

Now a number of models can be applied to the signal integrity analysis, including: IBIS (and its expansion – EBD), MOD (and expansion of this model – PML), SPICE. IBIS models found application in many systems of design, in particular, of P-CAD 200x, Altium Designer, Mentor Graphics HyperLynx and in others. Application of IBIS models allows to bypass the difficulties connected with creation and application of SPICE models of the integrated circuits which are based on the detailed description of internal structure of a product. In this work we discuss experimental methods of IBIS models creation. The main attention is paid to interpretation of measured I-V curves of digital integrated circuits input and output buffers. The basic structure of the output CMOS buffer of the digital scheme is the basis for IBIS model. One of the most difficult stages upon termination of physical measurements include the obtaining the corrected dynamic characteristics for creation of IBIS model. Along with simulations, the experimental methodology can significantly reduce complexity and time for IBIS models generation.

Keywords: signal integrity, IBIS models.

#### References

- 1. Baker B. The IBIS model: A conduit into signal-integrity analysis, Part 1. *Analog Applications Journal* (4Q 2010). Available at: www.ti.com/lit/an/slyt390/slyt390.pdf.

- 2. The IBIS Open Forum. IBIS Modeling Cookbook for IBIS Version 4.0. Available at: http://ibis.org/cookbook/cookbook-v4.pdf.

- 3. Low S. M., Shafdar M. H. Creating the IBIS model for a digital IC device. JURNAL FIZIK MALAYSIA, vol. 31, no. 1&2, 2010, pp. 1–4.

- 4. Lemeshko N. V. Development of a design method of radio engineering systems digital nodes using IBIS models of integrated circuits: Doct. Diss. Moscow, 2008, 122 p. (In Russian)

- 5. Petrosyants K. O., Kharitonov I. A., Adonon A. S., Sidorov A. V., Aleksandrov A. V. Digital circuit IBIS-models generation with account for temperature and radiation. Problems of Advanced Micro- and Nanoelectronic Systems Development, 2012, Moscow, Institute for Design Problems in Microelectronics of Russian Academy of Sciences, pp. 187–192. (In Russian)

- 6. CD4011B, CD4012B, CD4023B. Data sheet. Texas Instruments Incorporated, 2006.

Article history

Received 3 November 2017 Accepted 18 November 2017